Block

Your SoC Verification Solution

Block

Your SoC Verification Solution

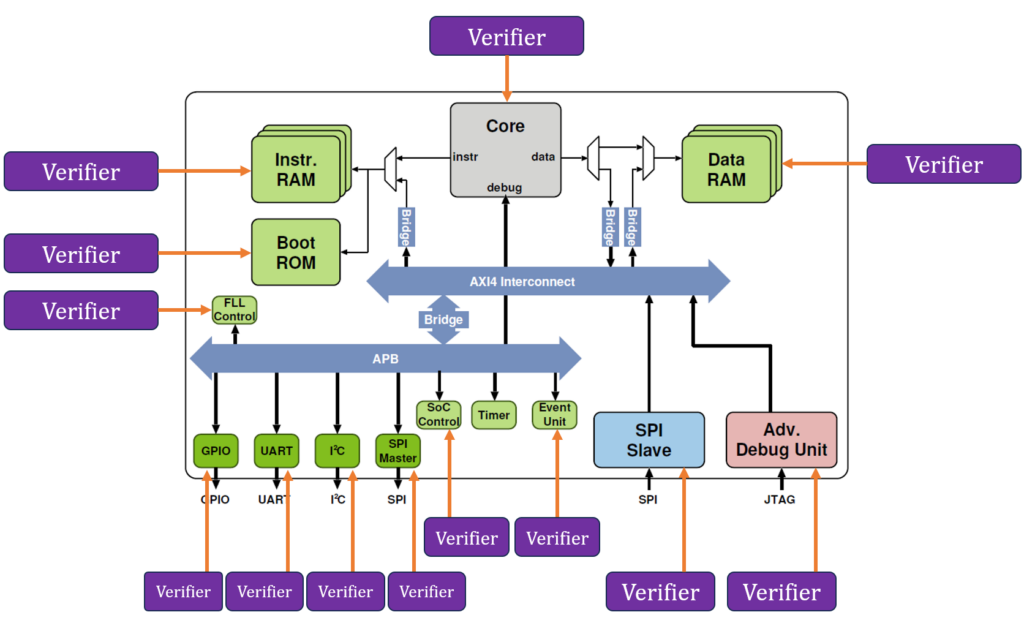

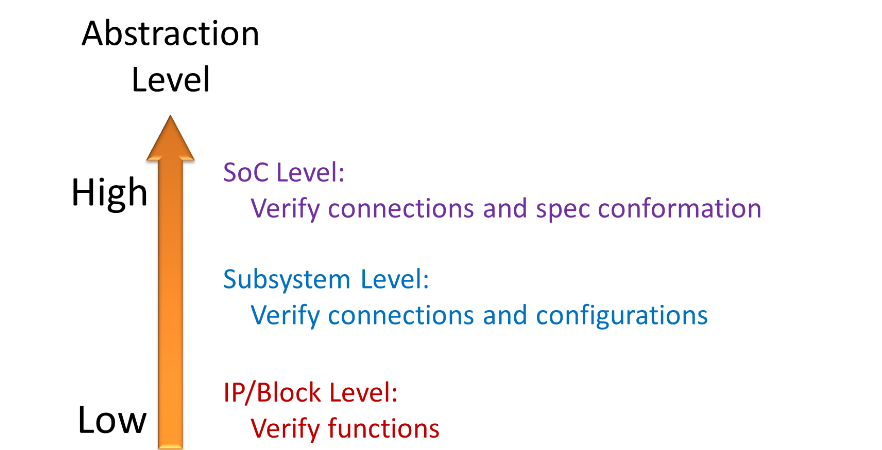

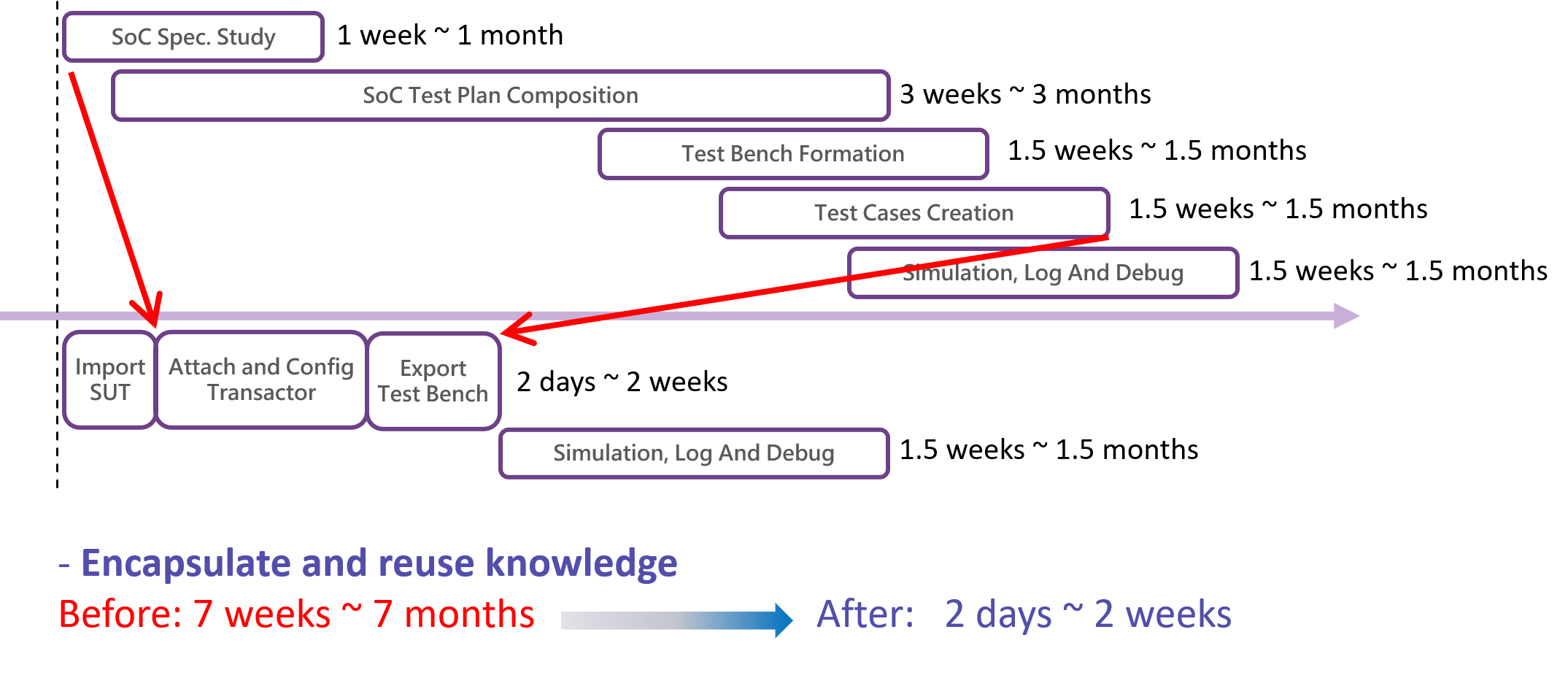

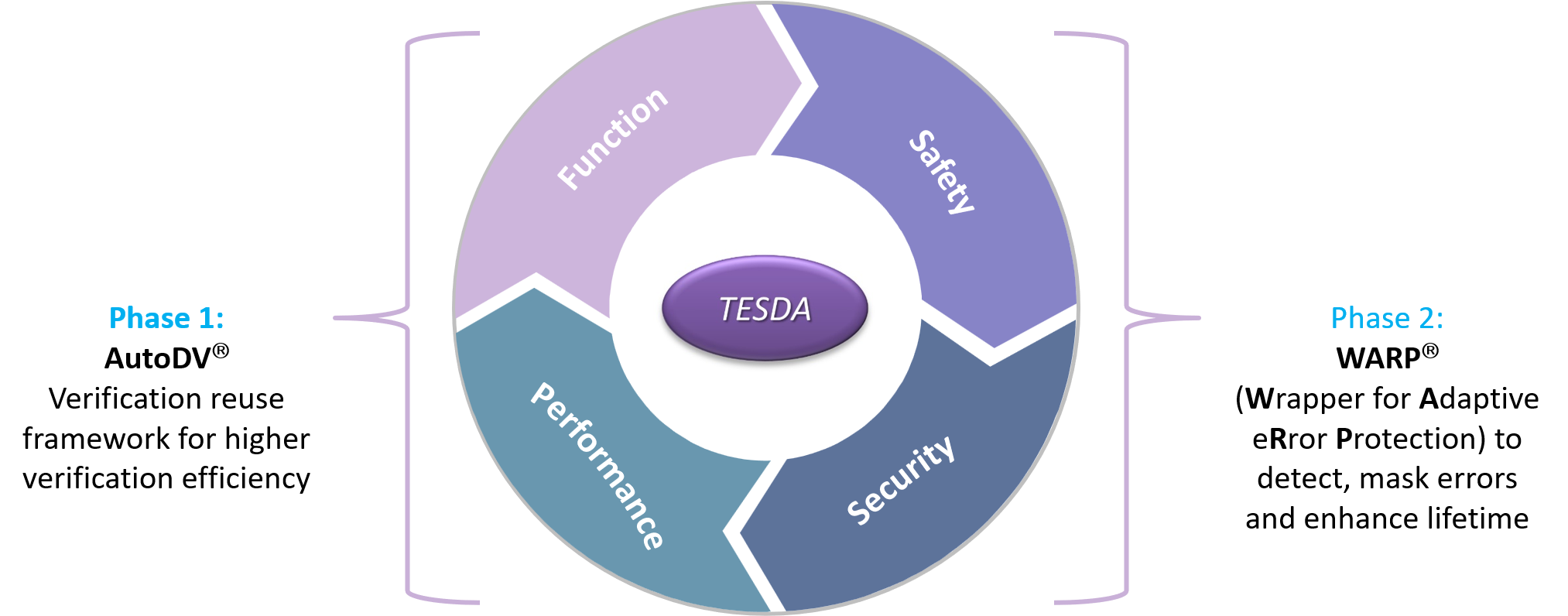

AutoDV is a TESDA Premier SoC Verification Solution providing a comprehensive set of advanced tools designed specifically for design and verification teams. With AutoDV, engineers can utilize its unified platform to take on tough SoC verification challenges without difficulty, offering automated solutions for SoC parsing, verifier integration, and verification platform creation.

AutoDV is meant to completely transform your verification process into a powerful tool. Imagine one single-experience platform that brings your whole team together, allowing you to share knowledge more efficiently and collaborate more effectively while seamlessly integrating your company’s internal methods. AutoDV does exactly that by transforming how you work.