At IP/block level, the main concern is functional coverage of individual IPs. While at SoC level, we assume all IP/blocks and subsystems within the SoC were well verified, and the goal becomes verification of functional coverage after integration of the IPs and subsystems and the performance coverage of behaviors of the SoC in comparison with the specification. TESDA focuses our technology development on the SoC level functional and performance coverage.

AutoDV is an ideal solution for SoC-level verification. By encapsulating and reusing past experiences, it significantly enhances the efficiency of verification. With AutoDV, you can encapsulate verification expertise at the SoC level and utilize the Transactor library as a framework for reuse by all users, thereby accelerating the verification process.

Built for electronic system design optimization

Revolutionary Technology

TESDA Explorer Suite® will fully leverage the traffic information gathered by Intelligent Scout® to optimize the system design by

–Knowledge abstraction

–Symptom identification

–Solution prescription

Engineering Services

Growth with Partners

TESDA not only provides complete education and training services for our employees, but also will provide this high-quality service to our external partners in the near future. This service will also fully integrate with our tools to provide the most efficient and valuable solutions to our partners.

Latest News

Issuer: Taiwan Electronic System Design Automation, Inc. (TESDA)

Release Date: January 20, 2025

Taiwan Electronics Design Automation Co., Ltd. (TESDA), a startup located in the Incubation Center of the Industrial Technology Research Institute, just raised NT$59.07 million to fund the development of its next-generation ASIC/SoC verification automation platform. Initially targeting NT$49.5 million at NT$22.5 per share, the round closed 20% oversubscribed, reflecting strong investor confidence in TESDA’s technology and services. Following this round, TESDA’s valuation reached NT$490 million, paving the way for a planned public offering and Emerging Stock Market listing in 2026.

Starting in 2025, TESDA will collaborate with Deloitte, one of the Big Four accounting firms, for financial audits and certifications. The company is also implementing robust internal controls in preparation for its IPO.

TESDA CEO Robert Chen highlighted that the funds will support the development of core technologies essential for tackling the growing complexity of SoC/ASIC design verification. TESDA’s AutoDV software drastically reduces resource requirements for complex SoC verification projects, cutting the time needed from 80-120 to just 16-24 person-months.

With a focus on automation, AutoDV addresses the IC industry’s chronic shortage of verification engineers, who require at least 10 years of experience to master the field. By leveraging cutting-edge automation, AutoDV accelerates tasks that would otherwise take weeks or months, helping companies complete projects with fewer resources.

R&D and innovation are at the heart of TESDA’s operations. CEO Robert Chen, who has won numerous accolades for his work at ITRI, including the Outstanding Paper Award and Best Paper Award at international conferences, continues to drive TESDA’s mission of achieving breakthroughs through academic-industry collaboration.

As markets for AI, robotics, autonomous vehicles, drones, low-Earth orbit satellites, and 6G communication expand rapidly, IC designers face growing challenges in meeting the surging demand for ASIC/SoC solutions. TESDA’s modular, reusable verification tools help clients save costs and significantly reduce development time, boosting efficiency and competitiveness in fast-evolving markets.

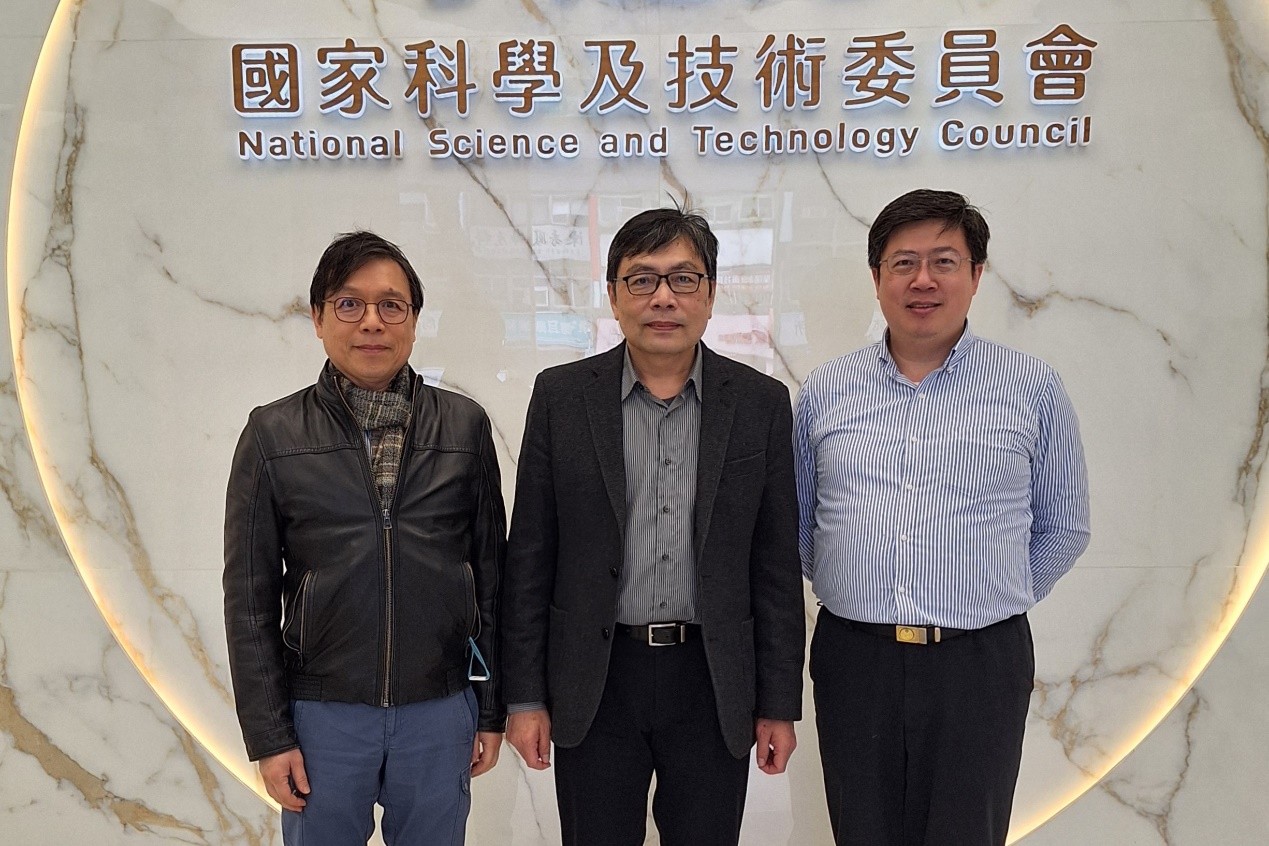

TESDA combines the R&D energy of academia with the practical experience of industry and is committed to pursuing R&D and innovative technological breakthroughs. From left to right in the picture are TESDA Chairman Kurt Huang, National Tsing Hua University Electrical Engineering Professor and Director of the Science and Technology Policy Research and Information Center of the National Research Institute under the National Science Council Huang Shi-Yu, and TESDA CEO Robert Chen.

TESDA combines the R&D energy of academia with the practical experience of industry and is committed to pursuing R&D and innovative technological breakthroughs. From left to right in the picture are TESDA Chairman Kurt Huang, National Tsing Hua University Electrical Engineering Professor and Director of the Science and Technology Policy Research and Information Center of the National Research Institute under the National Science Council Huang Shi-Yu, and TESDA CEO Robert Chen.

We’re thrilled to be a Gold Sponsor at DVConTaiwan2023! Join us on Sep 7, 2023, at NYCU, Hsinchu, Taiwan. Experience our upcoming SoC verification tool, AutoDV, and grab the chance to win a personal version on its official release!

Our CEO has also been invited to join the Steering Committee, engage with our talented team, and grab some exclusive giveaways. Let’s shape the future of tech together!

For more info, please visit: www.dvcontaiwan.org. We can’t wait to see you there!

In Partnership With

Providing dedicated and professional DV services for leading semiconductor manufacturers