Our Vision at TESDA

Driven by Moore’s Law, the semiconductor industry has experienced nearly 50 years of advancement and brilliance, but now we seem to have seen its limit. However, silicon-based semiconductor technology will remain mainstream for the foreseeable future, so there must be other ways to advance the overall performance of SoCs in addition to Moore’s Law. In view of this, TESDA aims to develop SoC level verification automation technology and link such technology with architecture-level optimization.

Further explanation follows

- Today’s advanced manufacturing process is expensive, and the progress of Moore’s Law is becoming more and more difficult. In addition, the power scaling predicted by Dennard’s law has stopped around 2005 due to leakage current and heat dissipation problems. Therefore, it is difficult for electronic system and IC design manufacturers to gain the advantages of chips in performance, power consumption and cost simply by relying on the evolution of the manufacturing process as in the past, thereby bringing the competitiveness of products. In light of this, industry pundits have discussed other possibilities for optimizing the design of future electronic systems, such as Heterogeneous Integration, new material systems (GaN, SiC, MRAM, RRAM, etc.), or optimization according to user scenarios and algorithms, i.e., Domain Specific SoC (DSSoC). Although there have been many discussions, SoC level verification and architecture-level optimization problems have yet to be completely resolved by the industry.

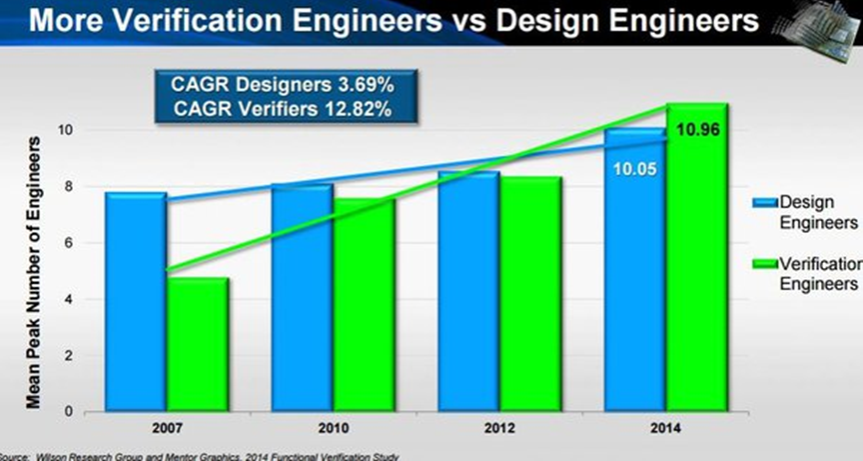

- After 20 years of hard work by the industry, SoC design has mostly been based on the assembling of reusable IP, coupled with hardware block design based upon the company’s proprietary algorithm and technology. In other words, although the complexity of SoC design is still growing exponentially, compared with the design space of verification and architecture exploration, the availability of required resources has not increased at a comparable pace. Figure 2 below shows that the current demand for DV is larger than that of IC designers!

Fig.2 More Verification Engineers vs Design Engineers

- After 20 years of hard work by the industry, SoC design has mostly been based on the assembling of reusable IP, coupled with hardware block design based upon the company’s proprietary algorithm and technology. In other words, although the complexity of SoC design is still growing exponentially, compared with the design space of verification and architecture exploration, the availability of required resources has not increased at a comparable pace. Figure 2 below shows that the current demand for DV is larger than that of IC designers!

- Modern RTL design may be able to achieve accurate simulation results for the SoC design, but the resources and time required for the simulation are so huge that it is simply impossible to carry out the simulation of the entire system. Therefore, under the pressure of the launch schedule, the product can only launch with limited verification results, allowing for a high level of risk to remain in the project. As RTL is gradually unable to meet the needs for the increasingly complex chip design, the optimization of design and verification at the architecture level (i.e. software and hardware co-optimization) becomes more urgent and important, and its importance can be seen from the changes in the system design behaviors of some large companies. For example: Facebook, Apple, Google, Tesla, Microsoft, Amazon, Alibaba, Huawei, etc., are no longer satisfied with the standard chips on the market, but design special chips according to the needs of their proprietary algorithms and services. However, due to the requirement of customization of the chip, the complexity of verification is continuously increasing, making an abstraction level higher than that of RTL a necessity.

- Based on the above, it is again stated that the electronic system level (ESL, Electronic System Level) design at a higher abstraction level has become the possible savior of the IC design method. We hope that during the verification process, we can first co-design both software and hardware and carry out optimization at a higher level of abstraction, and under different usage scenarios and their constraints, we can then explore cost, power consumption, performance, security and reliability. After analysis and trade-offs, we then find the best possible target system architecture, and subsequently carry out the detailed designing process. After Gary Smith started to promote this methodology around 2000, after the efforts of the industry, he also proposed the SystemC standard of IEEE1666, allowing for software and hardware to be described in a unified language (C++) framework. Based on this standard, EDA has introduced some system architecture simulation tools. However, it has been more than 20 years since Gary Smith advocated this process, and this design method is still not very popular. Why? Other than stated in DARPA ERI that “Enabl[ing] better hardware-software co-design and intelligent scheduling of applications and data on a heterogeneous processor, …, whereas today, … is a time-consuming, hand-tuned exercise”, there is still a lack of automated architecture synthesis tools! In addition, TESDA also found another important reason during the research process, being that its top-down electronic system architecture design methodology is incompatible with the current general bottom-up, IP-assembling SoC design methodology which leverages the vast reusable IP resources built up in the decades. For example, the equivalence of the SystemC model and RTL IP, the accuracy of the higher level system model, and the immaturity of the High Level Synthesis tools have made it difficult for designers to adopt the elegant top-down methodology.

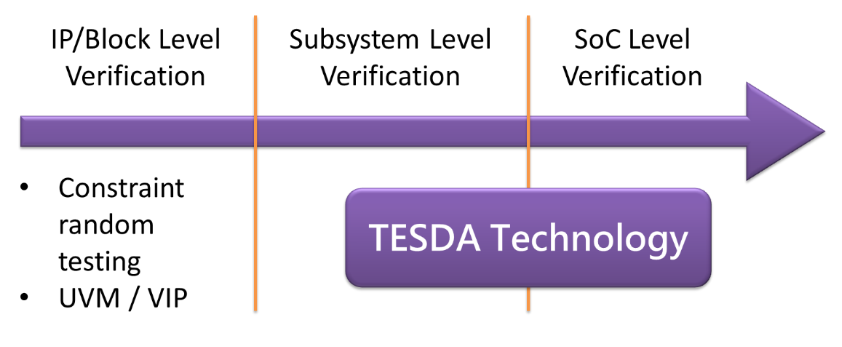

Therefore, TESDA believes that the methodology that can truly promote this architecture design should adopt the current bottom-up methodology as a basis, and then gradually transition upwards at later stages. At the same time, TESDA is also convinced that the abstraction level of design and verification must be raised to the SoC architecture level and the verification of IP and RTL level details must be avoided, so as to ensure the correctness of the SoC design within a reasonable time. Therefore, investing more automation technology in SoC-level verification and architecture exploration will be an inevitable trend in the future!

Such is the motivation behind TESDA’s incorporation and also the focus of TESDA’s research and technology.

- Based on the above, it is again stated that the electronic system level (ESL, Electronic System Level) design at a higher abstraction level has become the possible savior of the IC design method. We hope that during the verification process, we can first co-design both software and hardware and carry out optimization at a higher level of abstraction, and under different usage scenarios and their constraints, we can then explore cost, power consumption, performance, security and reliability. After analysis and trade-offs, we then find the best possible target system architecture, and subsequently carry out the detailed designing process. After Gary Smith started to promote this methodology around 2000, after the efforts of the industry, he also proposed the SystemC standard of IEEE1666, allowing for software and hardware to be described in a unified language (C++) framework. Based on this standard, EDA has introduced some system architecture simulation tools. However, it has been more than 20 years since Gary Smith advocated this process, and this design method is still not very popular. Why? Other than stated in DARPA ERI that “Enabl[ing] better hardware-software co-design and intelligent scheduling of applications and data on a heterogeneous processor, …, whereas today, … is a time-consuming, hand-tuned exercise”, there is still a lack of automated architecture synthesis tools! In addition, TESDA also found another important reason during the research process, being that its top-down electronic system architecture design methodology is incompatible with the current general bottom-up, IP-assembling SoC design methodology which leverages the vast reusable IP resources built up in the decades. For example, the equivalence of the SystemC model and RTL IP, the accuracy of the higher level system model, and the immaturity of the High Level Synthesis tools have made it difficult for designers to adopt the elegant top-down methodology.